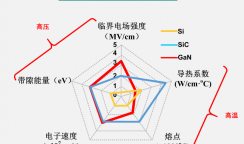

本文将描述在SoC设计方法中追求新过程的目的。该过程包括提取、评估和分析复杂SoC及其封装环境的全电磁耦合模型。分析强调了电磁耦合对现代复杂SOC设计性能和功能的影响。背景随着纳米尺度技术的引入,互连线的深宽比得到了提高。因此,来自相邻攻击者的容性串扰会对受害者网络产生更大的影响,这就需要新的改进的SoC设计流程。为了保证攻击者注入(静态)受害者网络的(累积)能量不会造成电路网络故障,我们需要一种全新的噪声分析工具和相应的IP表征方法。对静态时序分析流程中用于互连延迟计算的算法进行了扩展,反映了噪声对延迟的影响,这种影响是由于跃迁信号对攻击者的并发转换导致输出端可能发生波形变化而引起的。用于物理实现的EDA工具也包含新的特性。详细的布线算法已经被扩展,包括相邻互连的并行运行长度的限制。同时采用更复杂的噪声计算/避免方法来辅助布线轨迹的选择。设计师采用的技术旨在进一步降低后续容性串扰噪声故障的风险。此外,对关键网络的特定非默认布线规则(NDR)进行编码,以指导实施工具使用大于层上金属段之间的最小值的距离,或者将段引导到与非交换(电源/接地)网络相邻的轨道,从而有效地屏蔽段之间的耦合转换。金属段之间有限范围的电容电场线可以轻松纳入SoC物理设计和电气分析流程,并得到库单元输出驱动器波形和输入引脚噪声灵敏度模型(标准)的支持。随着SoC时钟频率目标的提高和纳米设计中电源电压的缩放,特定网络的(自)电感的影响变得更加明显。通过将提取的RLC模型应用于P/G网格,将开关电流源注入网格位置,并分析电源/接地噪声容限。此外,我们使用电感元件来分析时钟网络的转换速率,并对时钟驱动器转换的(谐波)高频内容呈现附加阻抗。参考文献中的例子描述了一种从金属段组中提取偏置电感的代表性方法——假设部分电感用于一个段,以减轻定义“全回路”电流返回路径的困难。但是时钟信号分布可能会受到影响。当今SoC设计的电磁建模要求现代SoC设计的复杂性集成了一组极其多样化的高性能IP,相应地增加了不同物理块之间电磁耦合的潜力。为了表示芯片上电流回路之间的互感和长距离相互作用,我们扩展了P/G门和时钟网络的隔离(部分)电感模型。上图说明了对这种物理耦合建模的重要性。设计中两个“隔离”的小环相距1毫米。当它们被完全提取出来一起分析时,它们是孤立的,耦合性很弱。该设计还包括第三个更大的20毫米x 25mm毫米的戒指。当考虑第三环路的RC效应时,它对两个线圈之间的隔离几乎没有影响。然而,当执行全电磁(EM)提取(RLCk)和分析时,从图中可以看出,由于额外的EM耦合,两个小环路之间的隔离在10GHz下降低了30dB。请注意,第三个环/环路在物理上并不与两个IP环路相邻,全电磁耦合不同于短距离电场容性串扰。(顺便说一下,为了证明EM耦合来自第三个周期,对第三个周期“切”做了额外的分析——返回给两个周期的结果是孤立的,如上图所示。芯片上有助于电磁耦合的周围结构包括许多可能性,如P/G栅极(带去耦盖)、密封环、大块硅衬底、封装上的再分布层金属等。那么,为什么会有SoC EM耦合的问题呢?上图显示,IP模块之间的隔离主要在非常高的频率下受到影响。考虑当前的SoC设计,其中许多串行收发器通道封装在一个芯片上,例如,这些SerDes通道可以以7GHz传输PAM-4 56Gbps信号。一组通道将共享一个公共VCO/PLL时钟源,多组通道将集成在一起,以提供所需的总数据带宽。(每组还可以有多个内部VCO,以跨越更大的传输频率范围。)多个SerDes通道、其P/G网络、密封环和封装结构之间的磁耦合可能导致时钟抖动显著增加,从而导致不可接受的误码率。如前所述,当今先进封装的拓扑结构是电磁耦合模型的关键部分。它需要在2.5D封装中包含再分配和功率传输金属(包括连接器)。在3D封装中,多个堆叠且变薄的模具的独特特征也需要EM耦合模型。EM耦合工具这就需要SoC团队在signature方法(sign-off)中加入EM耦合分析,这就需要新的工具/流程来帮助设计人员完成EM模型提取和仿真的艰巨任务。最近,我有机会与ANSYS的工程副总裁Yorgos Koutsoyannopoulos讨论最新的电磁耦合工具/流的进展。约尔戈斯说:“我们将电磁耦合分析任务分为两部分。最终目标是为设计者提供设计中所有相关结构的RLCk模型,并模拟电路级模型的时间、频率和噪声。”但是整个芯片封装的数据量会难以管理,SoC上的大部分ip信号都不会被关注。我们开发了一个评估流程来帮助设计人员确定具体的网络,其中可以进行详细的电磁耦合模型仿真。"对完整芯片封装模型的初步评价是什么?"约尔戈斯解释说:“使用ANSYS Pharos工具的评估过程侧重于评估SoC金属、过孔、电介质和基板模型,而不是考虑电路级细节。设计者对(顶层)互连层感兴趣,并构建拓扑模型以在物理断点处自动添加端口。在这个连接上,如果没有底层电路,就没有对提取的RLCk模型的注释——芯片不需要LVS低速扫描。为了检测更大的周期,分析将跨越SoC IP物理层次。我们的目标是找到交互结构,以确保进一步和详细的模拟。”“会给设计师什么反馈?”yorgos:“ANSYS Pharos在切割布局的数据库上提供了两个通用的热图,用于相关的视觉反馈,并为后续的模拟选择网格。移除的模型根据设计者提供的频率范围(和增量)进行评估。”s“即使去掉SoC模型,它仍然是海量的物理数据——什么样的IT资源需要这种早期评估?”比如一个100mm**2的晶圆,上面有五层金属层,在64核1TB内存占用服务器上,每个频点的热图大概需要1-3个小时。”约尔戈斯回答道。我觉得还不错。)Yorgos:“Pharos使用了与其他工艺相同的互连技术,包括将金属片电阻率定义为线宽和工艺角度的函数。对于具有封装模型的晶片,我们可以将封装堆叠定义和再分布层包括到统一的提取模型中。我们还有一种先进的方法,可以将模具底板塑造成非常精确的钢筋混凝土网格网络。“就像扩展设计方法以支持容性串扰的影响一样,高性能SoC IP(可能使用高级封装)将越来越需要采用广泛的电磁耦合分析方法。参考文献: [1] Ruehli,A.E .,《复杂环境下的电感计算》,IBM研发杂志,第470-481页,1972年9月。 White等人,“FASTHENRY:多极加速三维电感提取算法”,IEEE微波理论与技术汇刊,第42卷,第9期,第1750-1758页,1994年9月。全名是非默认路由规则,它不是默认路由规则。设置时钟路由的一般规则。时钟的翻转频率高,对时钟路径的串扰和EM影响也大。因此,通常采用双倍宽度的卷绕宽度。默认的缠绕规则是单位宽度,单位宽度是指技术lef中定义的金属层宽度。如果我们需要采用双宽度路由规则,那么我们需要在工具使用该规则之前定义NDR。对于NDR,我们可以在LEF中定义它,也可以直接用命令来定义。电磁耦合 Restle,p .和Deutsch,a .,“设计最佳时钟分配网络”,VLSI电路研讨会,第2-5页,1998年。 Raman,a .等,“SoC设计中的电磁串扰失效与症状”,2017第十八届微处理器与SoC测试与验证国际研讨会,第39-43页。[5] Papadopoulos,p .等,“SoC电磁串扰的挑战与趋势”,第20172届国际验证与安全研讨会(IVSW),第63-69页。专业术语解释: NDR [/S2/]

[2][3]

[4]电磁耦合又称互感耦合,它是由于两个电路之间存在互感,使一个电路的电流变化通过互感影响到另一个电路。两个或两个以上的电路元件或电网络的输入与输出之间存在紧密配合与相互影响,并通过相互作用从一侧向另一侧传输能量的现象;概括的说耦合就是指两个实体相互依赖于对方的一个量度。

在线

在线

咨询

咨询

关注

关注