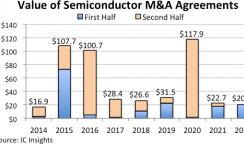

封装作为芯片制造过程的最后一步,在电子供应链中看似不起眼,却一直扮演着至关重要的角色。作为处理器和主板之间的物理接口,封装为芯片的电信号和电源提供了一个着陆区。特别是随着行业的进步和变化,高级包的作用越来越突出。随着半导体工艺和芯片架构的日益复杂,二维单芯片SoC的传统思路已经逐渐不可行,多个小芯片的小芯片封装已经成为大势所趋。所以要想延长摩尔定律的寿命,只能解决后端“包装”技术的瓶颈,在这个领域部署重兵。最近,业界看好先进MCP的设计,并计划迅速加速其发展。

虽然英特尔将10 nm制程技术推迟了4年,导致全球芯片制造老大拱手让给了TSMC,但从2019年开始,英特尔发起了绝地反击,从封装开始。此前,英特尔已经宣布了六大技术支柱,其中工艺封装是最底层的支柱,封装正在成为产品创新的催化剂。

近日,英特尔在上海召开发布会,分享了三大封装新技术架构,强调可以同时提供2D和3D封装技术。

英特尔集团副总裁、封装测试技术发展部总经理Babak Sabi强调:英特尔是一家垂直整合的IDM厂商,在六大技术优势中,所有领域都有技术细节。这也给了英特尔无与伦比的优势。从晶体管到整体系统级的集成,英特尔可以提供全面的解决方案。在异构集成时代,英特尔作为IDM,非常注重开发方案。我希望所有的英特尔产品都能轻松集成到客户的平台上。

Babak Sabi介绍了英特尔封装测试的全过程。一般来说,芯片的封装测试会经历以下几个步骤:

人们已经花了很多时间来研究英特尔多芯片封装体系结构(MCP)。英特尔院士、技术开发部联席总监Ravi Mahajan解释了他们对MCP的愿景:他们希望在封装中集成多种功能,实现芯片和小芯片之间的连接,同时可以帮助整个芯片实现单芯片系统和片上系统(SOC)的功能。因此,低功耗和高带宽的高密度互连对于实现这一愿望至关重要。马哈詹解释说,为了做到这一点:

1。轻薄紧凑的客户端包;

2。多个节点的混合封装;

3。高速信号传输;

4。互连小型化(高密度、高带宽);

这些将是未来技术发展的重点。

至于传输信号,是在整个半导体和芯片表面上传输的,会受到金属表面粗糙度的影响,可能会随着整个信号的传输而丢失。英特尔的特殊制造技术将大大降低金属表面的粗糙度。同时采用了新的布线方式,降低了两者之间的串扰。此外,Intel还采用了全新的空槽布线生产工艺和流程,通过介质堆栈的设计,可以进一步降低它们之间信号传输的损耗。

此外,对于高密度高带宽互连技术,Ravi Mahajan指出可以分为两个裸芯片堆叠在一起的3D互连和两个裸芯片水平连接的2D互连。对于3D互联来说,导线数量相对较少,速度相对较快,而另一种则正好相反。与串行传输和并行传输相比,并行传输将大大减少延迟,提高其速度。好的设计,整个能耗甚至可以降低10%左右。为了做到这一点,需要配合先进的封装技术,这也是英特尔开发封装技术的重要原因。

基于此,英特尔三大新包装武器呼之欲出……

MDIO——一种新的芯片间接口技术

基于高级接口总线(AIB)物理层互连技术,英特尔发布了这种新的芯片间接口技术,称为MDIO。MDIO技术支持小芯片ip模块库的模块化系统设计,更加节能,响应速度和带宽密度可以是AIB技术的两倍以上。马哈詹强调,这些新的封装技术将与英特尔的制造工艺相结合,成为芯片架构师的创意调色板,他们可以自由设计创新产品。

据了解,MDIO是一种性能更好的芯片间接口(pin)技术。与英特尔以前使用的AIB(高级接口总线)技术相比,MDIO可以在更小的连接区域内实现更高的数据带宽。这样即使是ODI技术中更细的引脚也能满足芯片间数据带宽的需求。

通过在连接方式、连接层、连接引脚等影响芯片堆叠的细节上进行全面的技术创新。,英特尔终于实现了在单个基板上横向和纵向封装更多芯片的愿景。

ODI—全方位互联技术

为了进一步提高水平和垂直堆叠的灵活性,英特尔还引入了额外的物理互连层技术——ODI。该技术为封装中小尺寸芯片之间的全方位互连通信提供了更大的灵活性。ODI存在于基板和芯片之间。在这一层上,英特尔可以埋线,排列连接引脚,密度远高于传统封装技术。从而在保证芯片电源的情况下实现更高的互连带宽。

ODI技术有两种,分别对应于单芯片和多芯片的互连。

emib嵌入式多芯片互连桥

当谈到2D芯片封装和芯片之间的互连时,我们通常会考虑它有多薄,其次是几个芯片之间的间距。通过在传统的有机封装中加入先进的制造技术,每平方毫米的导线密度可以增加到100-150。英特尔的EMIB(嵌入式多芯片互连桥)技术可以实现更好的线密度。Mahajan介绍说,嵌入式多芯片互连桥(EMIB)使用一小块硅在MCP中的两个芯片的相邻边缘之间提供自由互连。EMIB目前集成了四个金属化平面——两个信号和两个电源/地(主要用于屏蔽,但也用于芯片之间的P/G分配)。

Mahajan提供了关于EMIB的其他技术信息。他指出,EMIB平面的金属厚度介于硅片的RDL层和封装走线之间,实现了互连间距和损耗特性的平衡。“我们现在有2um的线宽和2um的线间距,并且正在向1um的线宽和1um的线间距努力。我们对EMIB的Si分析表明,长达8mm的长度仍然可以提供足够的眼余量。从概念上讲,EMIB可以达到~ 200mm2。”(例如,相邻芯片边缘之间的距离为25 mm,宽度为8 mm)。

一种新的3D封装技术——FoverOS

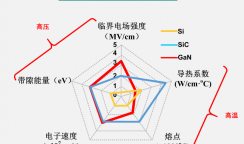

3D封装技术可以将产品分解成更小的“小芯片”,其中的功率传输电路、SRAM和I/O元件可以内置在底层的basedie中,而高性能的逻辑芯片则堆叠在上面。同时,Foveros还可以在新的设备设计中灵活地混合和匹配各种硅知识产权模块、各种存储和I/O组件。

Foveros技术最让业界着迷的地方在于,它可以省去过去重新设计、测试、流片的漫长流程,直接将不同品牌、不同IP、不同工艺的各种成熟解决方案打包在一起,从而大大降低成本,提高产品上市速度。同时,集成度的提高可以进一步缩小整体方案的体积,为万物的智能化和网络化打开一扇全新的大门。

Co-EMIB

Co-EMIB采用高密度互连技术,将EMIB(嵌入式多芯片互连桥)2D封装与Foveros 3D封装技术相结合,诞生了能够实现高带宽、低功耗和具有竞争力的I/O密度的co-EMIB。Co-EMIB可以连接更高的计算性能和能力,互联两个或两个以上的Foveros组件,基本实现SoC性能,连接模拟器、存储器等模块,具有非常高的带宽和非常低的功耗。

Mahajan总结说,整个行业都在不断推动先进的多芯片封装架构的发展,以更好地满足高带宽和低功耗的要求。英特尔拥有多项关键基础技术,包括EMIB、Foveros和Co-EMIB,这些技术是MCP高密度实施的关键。英特尔不仅有物理层技术,还有先进的IO技术和高密度封装技术,可以一起设计。

芯片小型化有多难?英特尔指出了三个方向

互联技术的封装方式主要有两种:一种是将主要的相关功能集成在封装上。其中一种是将调压单元从主板移到封装中,可以实现完全集成的调压封装。另一种方式是分解SOC片上系统,将不同功能属性的小芯片连接起来,放在同一个封装中。通过这种方式,我们可以实现接近于单个芯片的特性和功能。

英特尔封装研究事业部元器件研究部总工程师Adel Elsherbini解释道:无论我们选择哪种实现路径,都需要实现异构集成和特殊的带宽要求,而异构集成和特殊的带宽要求也可以帮助我们实现更高密度的多芯片集成。

为此,英特尔指出了小型化技术的三个方向:

1。用于堆叠管芯的高密度垂直互连可以大大增加带宽,同时可以实现高密度管芯堆叠。

2。未来随着小芯片的使用,全球水平互连将越来越普及。

3。全方位互联,可以实现以前无法实现的3D堆叠带来的性能。

高密度垂直互连

Adeelsherbini介绍,高密度互连技术除了高带宽和低延迟之外,还将带来更多优势。随着芯片尺寸越来越小,每平方毫米的导线接头会越来越密。为了保证带宽,晶体管之间的距离会越来越短,而传统的焊料技术已经接近极限,于是一种全新的技术——混合键合诞生了。采用这种技术,芯片间距可以达到10微米,桥突起和互连密度会更好。

完全横向互连

英特尔希望在整个封装层面实现小芯片的互联。作为一种水平互连技术,应该考虑线性间距。随着线间距越来越短,同样的面积可以安装更多的硅片,信号之间的传输距离也会越来越短。使用有机中间层是更好的解决方案,因为它比硅成本低。但是使用有机夹层有一个缺点,就是需要激光打孔。通过光刻限定的通孔使得导线和通孔的宽度相同,从而不需要焊盘来连接,这可以在不牺牲传导速度的情况下完成。

全向互联

ODI技术可以保持上下基模的带宽速度快;另外,封装的电源可以直接由上层小芯片获得,不需要中间通孔;与传统技术相比,底模的面积大于安装小芯片的面积之和。这种并排互连可以将延迟降低2.5倍,功耗降低15%,带宽增加3倍。

Adeelsherbiny表示,未来除了Co-EMIB,英特尔还将考虑整合ZMV和Feverous或者EMIB和ZMV,以丰富技术路线。

无论是高密度垂直互连、全水平互连还是全方位互连,这三种互连方式都可以提高每立方毫米的功能,达到类似于单芯片的性能。

英特尔的新未来

英特尔围绕其在半导体技术和相关应用方面的能力构建了六大技术支柱,以支持其“以数据为中心”的战略,从而应对未来数据量爆炸式增长、数据多样化和处理方式多样化的挑战。

半导体晶圆堆叠技术的出现,让英特尔看到了新的方向。通过将不同功能、不同IP的芯片封装在一起,数据中心未来有望大幅简化架构,严格限制芯片内计算类型的拆分,从而在更大层面上实现统一。这完美解决了拆分计算架构带来的管理和运营挑战。然而,3D叠加技术仍然存在许多困难。未来,在这场马拉松比赛中,将由英特尔制定战略。

在线

在线

咨询

咨询

关注

关注