降低RC延迟,提高芯片运行速度

在积体电路中,「电阻─电容延迟时间」(RC Delay)是影响半导体元件的速度或性能的重要参数之一。随着半导体制程推进至7 纳米,不仅金属连线(interconnect)层数越趋增加,导线间的距离也不断微缩;当电子讯号在层数非常多的金属连线(interconnect)间传送时,其产生的「电阻─电容延迟时间」(RC Delay),将严重减低半导体元件的速度。如何降低「电阻─电容延迟时间」(RC Delay)、增加半导体元件运行速度,是一重要课题。IC工艺小型化,阻挡层有相对增加电阻的风险

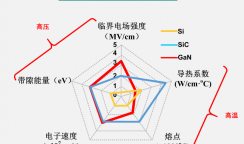

铜(Cu)和铝(Al)是半导体后段制程(Back End Of Line,BEOL)金属连线(Interconnect)最常使用的金属材料。而铜主要会被用于先进制程的「金属连线」,来自于铜导电性比铝好,不过铜(Cu)原子在介电层的扩散系数远比铝原子大,为防止铜(Cu)扩散在介电层所造成线路短路。所以,在半导体制程,就必须使用更致密的「氮化钽」(TaN),取代柱状晶结构的「氮化钛」(TiN),借此避免铜扩散。然而,此氮化钽(TaN)比氮化钛(TiN)的电阻系数大很多,相差十倍以上(参见表1),使用氮化钽(TaN)为铜的阻障层,将会有使金属连线电阻增加的风险。▲ 表1:TaN 及TiN 电阻系数。金属线上的电阻为「铜线电阻」加「氮化钽(TaN)层电阻」的总和。铜线尺寸大时,氮化钽(TaN)层引起的电阻增加比例不大,可忽略不计。但是当芯片微缩到非常小,促使铜线的尺寸也逐渐缩小时,氮化钽(TaN)层贡献的电阻比例就愈来愈大。宜特材料分析实验室使用并联电阻简化计算氮化钽层电阻贡献度(见表2)。铜线横截面尺寸由200 纳米降到20 纳米,则氮化钽层电阻贡献度约增加大于40 倍。▲ 表2:氮化钽层电阻贡献度,利用并联电阻简化计算。然而,在铜(Cu)制程中,因铜的容易扩散的特性关系,所以也不能藉由降低氮化钽(TaN)层的「厚度」来减少电阻,否则就会失去阻障功能。因此在7 纳米IC 制程中,使用新材料取代铜导线或阻障层变成很重要的课题。要降低7 nm芯片的电阻,金属材料的选择是关键

那该如何减低氮化钽(TaN)层的电阻呢?调整该层的金属材料就成为关键。经研究,发现金属钴(Co)是加入氮化钽(TaN)阻障层的极佳候选材料,钴(Co)不但降低阻障层的电阻,而且可以降低阻障层厚度,一举两得。双层接触窗设计允许钴(Co)发挥最大效率

金属导线和矽基板上半导体元件之间的连结称为接触窗(contact),主要是靠钨(W)连结,其阻障层材料是氮化钛(TiN)。在铜金属化制程中,如何降低W / TiN 的接触窗的电阻,钴(Co)又成为最佳候选者。但是,用钴(Co)直接完全取代W / TiN 直接和铜接触,则铜和钴容易固溶在一起,造成金属导线电迁移性能会变差。于是有了双层接触窗的制程设计。测量7 nm工艺芯片以观察钴(Co)是否完全取代铜(Cu)

剖析完为什么要使用钴(Co)的原因后,宜特材料分析实验室进行实测,一起来看看钴(Co)是用在7 纳米制程芯片的那些地方?钴(Co)真的完全取代铜(Cu)了吗?样品前准备为了开展7 nm先进工艺产品的分析,亿特材料分析实验室购买了市面上手机的相关零部件,获得了麒麟980 CPU。由于这款CPU封装在手机电路板上,需要拆下相关零件,分析相关结构,包括x光分析、去焊球、去封装、去胶、红外定位、研磨、吃酸、CPU/DRAM双芯片分离等技术。最后得到麒麟980芯片。

TEM实际观察依特材料分析实验室使用透射电子显微镜(TEM)和高性能能量色散X射线能谱仪(EDS/EDX)。因此,对7 nm芯片的前端制程(FEOL)和后端制程(BEOL)进行了分析。材料分析实验室要通过TEM和EDS观察芯片结构中的第一(M1)和第二(M2)金属层,分析7 nm FinFET、栅极、触点(见图2)以及相应的钴(Co)和钨(W)的成分分布(见图3)。▲图2: Stemha ADF图像,显示鳍晶体管、栅极、接触窗、M1和M2等。▲图3:桃色由钴(Co)组成,草绿色由钨(W)组成。通过对比图2,可以知道钴和钨在结构中的分布。通过对比图2和图3两幅图,在亿特材料分析实验室观察到钴(Co)成为“接触窗”和“阻挡层”的材料,钴(Co)覆盖第一(M1)铜金属层的整个结构,成为阻挡层的材料。然而,Co并没有完全取代接触窗的W/TiN。可能是因为接触窗工艺和阻挡层工艺采用不同类型的工艺,导致Co与周围材料的反应条件不同,使得接触窗的Co不能完全替代W/TiN。结论

TEM结果显示钴(co)没有被用来代替铜(Cu)。在铜的阻挡层中使用钴,并且仅替换接触窗口的一半。因此,亿特材料分析实验室可以证明,在7 nm先进工艺产品中,钴(Co)并没有完全取代铜(Cu)。

在线

在线

咨询

咨询

关注

关注