随着集成电路的小型化,工艺技术的发展在穿孔、光刻、隧穿和散热等方面遇到了越来越多的技术瓶颈。为了继续推动芯片性能的提高,世界领先的半导体制造商提出了不同的想法,包括在器件结构、材料和封装方面的创新。此时,Chiplet开始走上舞台,承担起一个大角色,但挑战依然存在。2021年伊始,让我们回顾一下Chiplet的风雨历程和未来征程。

分而治之,小芯片有助于解决工艺集成的问题

总的来说,小芯片技术是SoC集成发展到一定程度后的一种新的芯片设计方法。它将SoC分成更小的管芯,然后将这些模块化的小芯片(管芯)互连起来,采用一种新的封装技术,将不同功能、不同工艺的小芯片封装在一起,成为一个异构的集成芯片。

小芯片的概念是10多年前提出的。为什么最近变热了?厦门大学闽江学者、微电子与集成电路系主任俞大全教授,博士,特聘教授,认为小芯片技术的概念最初是从2.5D/3D IC封装发展而来的,用2.5D的穿硅通孔集成CPU/GPU和存储器都可以归为小芯片。2013年,TSMC和Xilinx联合开发的FPGA就是一个典型案例。随着摩尔定律的进一步放缓,工艺升级的难度越来越大,尤其是进入几纳米的工艺后,只有少数代工厂可以做到。在这种情况下,业界对小芯片技术寄予厚望。芯片异构集成封装在一起,有望解决工艺改进困难带来的芯片性能成本问题。

这一点从AMD EPYC(骁龙)处理器就可以看出来,它凭借小芯片技术取得了巨大的成功。

AMD EPYC处理器混合多芯片架构来自:AMD

正是小芯片技术,AMD EPYC处理器成功实现了64核高性能服务器芯片的集成。如果采用以前的单芯片设计,在现有技术下不现实,也不经济。AMD按照功能需求划分成小芯片,采用最优设计工艺制造,不仅可以降低成本,提高良率,还可以设计多核复杂大芯片。同时,模块化的设计思路也可以提高速度,降低芯片的研发成本。

俞大全教授表示,以前的SoC芯片设计是系统的整体设计,而现在的小芯片技术可以将CPU这样的大型芯片按照功能划分成不同的功能模块,分别设计制造,根据需要选择合适的封装技术进行系统集成,从而实现一个系统芯片的功能。

这似乎也应验了那句老话,“天下事,若久矣,总在一起。”看来在芯片设计的道路上,分而治之,进而实现更高更复杂的集成也是螺旋路上的必经阶段。

实现小芯片技术的两大挑战:互连和封装

然而,将几个小芯片互连并最终集成到一个大芯片中,面临着诸多技术挑战,其中互连和封装是需要克服的两个最重要的“壁垒”。

可以说,如何使裸芯片之间高速互联是实现小芯片技术的关键,这对芯片设计公司和整个产业链都是一个新的挑战。

光互连论坛(OIF)定义的电气I/O标准显示,在超短距离和超短距离链路上(芯片到芯片互连),数据传输速率高达112Gbps。芯片设计公司在设计裸芯片之间的互连接口时,首先保证高数据吞吐量。此外,数据延迟和误码率也是关键要求,能效和链路距离也要考虑。

在互联互通方面,设计厂商各有绝招。Marvell在引入模块化芯片架构时采用了Kandou总线接口;NVIDIA针对GPU的高速互联NV link方案;英特尔向外界免费授权的AIB高级接口总线协议;AMD推出的Infinity Fabrie总线互连技术,以及用于存储芯片堆栈互连的HBM接口...这些都是芯片设计公司实现高速互联的不同尝试。

在封装层面,包括英特尔、TSMC在内的巨头都在布局。

英特尔在异构互联的道路上进行了长期投资。多年前推出了EMIB技术,最近又推出了Foveros3D立体封装技术。不同于以往逻辑芯片和存储芯片的简单连接,Foveros可以将不同的逻辑芯片堆叠连接在一起,可以将不同工艺、架构、用途的IP模块、各种存储器、I/O单元“混搭”在一起。

基于Foveros 3D封装技术,英特尔推出了核心处理器“Lakefield”,其中CPU和GPU核心采用10nm工艺制造,I/O部分所在的基础层采用22nm工艺制造。

作为代工巨头,TSMC自然押下了重注。

一年前,TSMC展示了一款基于ARM核、采用Chiplet概念设计的芯片产品,采用TSMC 7nm工艺、LIPINCON互联和CoWoS封装技术制造。LIPINCON是一种高速串行总线,是TSMC多年前开发的一种裸芯片之间的数据互联接口技术。CoWoS是TSMC推出的2.5D封装技术,被称为晶圆级封装。它以芯片间共享基板的形式将多个裸芯片封装在一起,主要用于封装高性能大芯片。

台积电考沃斯3D封装示意图来自:Tsmc

基于TSMC小芯片概念的成功设计为行业带来了示范效应。对于那些想用Chiplet概念设计芯片,但又无力开发自己的芯片接口的无晶圆厂厂商来说,采用TSMC现成的接口LIPINCON IP无疑会很有吸引力。

多通道并行助推中国小芯片技术发展

国际巨头纷纷排队,国内厂商自然要在未来的小芯片层面“迎头赶上”。

俞大全教授认为,从广义的小芯片来看,比如CPU/GPU+内存通过硅片经中间层集成,国内厂商已经在跟进,比如华为海思、中兴等。,并且已经实现了一定量的量产。当然,OEM仍然是由TSMC和其他企业来做。从狭义的角度来看,一个SoC被分成几个小芯片,然后通过硅通孔(TSV)异质集成。目前,实施这一做法的公司数量相对有限。在未来,估计这项技术将由苹果等大公司推动,由TSMC等代工公司制造和集成。

另一方面,目前国内小芯片技术的制造和封装能力还比较落后。俞大全教授指出,这种封装技术越来越接近以前的制造技术。他认为,在高端封装技术领域,前封装时代正在快速到来。

不过,俞大全教授也表示,现在是中国发展先进封装技术的好时机。对于SMIC等国内领先的半导体制造企业来说,被美国制裁后,先进工艺的研发可能会受到限制。在这种情况下,先进封装技术的发展可能提供另一种可行的途径。

除了SMIC,国内从事封装制造的厂商也在关注推进先进封装技术的部署,尤其是3D芯片堆叠封装。紫光、武汉新芯、方静科技、硕贝德等厂商都取得了不错的成绩。

据俞大全教授介绍,他在厦大的工作是先进封装技术的研究,重点是小芯片的关键技术。他的研究方向包括TSV、TGV、芯片堆叠、新型键合方案等。目前正在申请一些专利技术。

此外,围绕小芯片技术实现的标准制定也引起了国内厂商的关注。

在IC CHINA 2020大会上,鑫苑董事长戴为民也极力推荐小芯片技术。他认为,Chiplet这种不同工艺节点的裸芯片混合封装的新形式是未来芯片发展的重要趋势之一,它将给整个半导体产业链带来新的机遇。作为IP供应商,芯元提出了IP as a Chip(IaaC)的概念,旨在用Chiplet实现特殊功能IP从软到硬的“即插即用”,解决7nm、5nm及以下工艺中性能与成本的平衡,降低更大规模芯片的设计时间和风险。戴为民特别强调了封装和互联对小芯片的重要性,尤其是芯片的互联,需要一致的协议,这就涉及到标准。

因此,有必要建立小芯片产业联盟。在2020年全球硬科技创新大会上,核心技术CEO敖海、中科院院士姚期智、紫光存储CEO任启伟等共同发起了小芯片产业联盟。动能科技CEO敖海认为,小芯片技术对于突破ai、CPU/GPU等大型计算芯片的计算能力瓶颈具有重要的战略意义,是解决中国高质量发展进程中晶圆技术“瓶颈”问题的关键技术之一。芯科科技作为国内一站式IP和芯片定制领导者,推出了INNOlink Chiplet、HBM2E等高性能计算平台技术,为国内自主标准,支持高性能CPU/GPU/NPU芯片和服务器。

除了封装和互连,支持小芯片芯片设计的EDA工具链以及生态是否完善和可持续发展也是小芯片技术成功需要解决的关键问题。

如今,中国芯片产业正处于新的窗口机遇期。小芯片这种新型设计技术的出现,无疑是国内集成电路产业奋起直追的有利时机,但这需要全行业培育从架构、设计、晶圆到封装、系统的一整套解决方案。

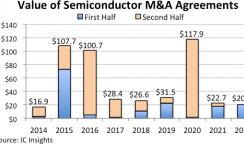

根据Omdia的数据,2018年Chiplet的市场规模为6.45亿美元,预计到2024年将达到58亿美元,到2035年将超过570亿美元。

面对全球市场下一个小芯片的井喷式增长,中国集成电路产业能否抓住机遇,分得一杯羹?从而提高我国高性能芯片中半导体的制造能力?现在是关键时刻。

在线

在线

咨询

咨询

关注

关注