对于那些不能在硅片上自然集成的IP,封装是最紧凑的异构集成平台,但稳定的增量改进是唯一可预见的前进方向。

先进的封装技术往往不是顶级芯片制造商的首选,但英特尔正试图将这一领域定义为关键领域之一,以帮助他们抵御摩尔定律的紧迫影响。

在组件层面推动创新可以提高异构性、连接性和带宽,同时降低功耗。在这个领域,英特尔一直比其他公司做得更好。

在过去的十年里,为了跟上经济和技术挑战的步伐,英特尔开发了许多技术。许多最重要的发展都发生在互联层面。例如,EMIB已经存在了十多年,它允许本地连接。对于高密度连接,它们也可以卷成硅插入管。Foveros还可以叠加3D和2D叠加功能,可以拼接在一起创建放大和扩展架构,更不用说全向互联的能力了。

在这段时间里,整个芯片行业也出现了几个关键的转折点。从电路板到天线的互连;从陶瓷到铜/有机物;从铅基焊料过渡到无铅焊料;从针格到线格。所有这些更广泛的技术都是Ravi Mahajan在英特尔任职期间开发的。在2000年进入互连领域之前,Ravi Mahajan首先开发了热机技术,这恰好是另一个重要的变化,推动英特尔在21世纪初开发了EMIB:从串行世界到以并行为中心的概念。这为我们今天拥有的高密度互联打开了大门。

今天,英特尔拥有各种封装形式的芯片:

封装越来越薄,超薄核非核封装。

英特尔EMIB技术,一种高密度2D封装技术

EMIB技术:全称为嵌入式多管芯互连桥,意为“嵌入式多管芯互连桥”。

EMIB是一种高密度2D平面封装技术,可以灵活组合不同类型、不同工艺的芯片ip,类似于一个松散的SoC。

高密度3D封装,单芯片间距50μm。

Foveros技术:首次为处理器引入3D堆叠设计,这是大幅提升多核和异构集成芯片的关键技术。

由于3D堆叠,Foveros具有更高的封装密度和集成度。2D EMIB封装的管芯间距可以是55微米,未来只能缩小到30-45微米。3D Foveros现在可以做到50微米的间距,未来可以进一步缩小到20-35微米(有焊料)甚至20微米以下(无焊料)。

集成2D和3D封装的英特尔Co-EMIB技术

Co-EMIB技术:通过使用高密度互连技术,EMIB(嵌入式多芯片互连桥)2D封装和Foveros 3D封装技术相结合,实现了高带宽、低功耗和颇具竞争力的I/O密度。

Co-EMIB可以连接更高的计算性能和能力,互联两个或两个以上的Foveros组件,基本实现SoC性能,连接模拟器、存储器等模块,具有非常高的带宽和非常低的功耗。

Foveros 3D封装是英特尔在今年年初的CES上提出的一项全新技术。它首次引入了CPU处理器的3D堆叠设计,可以实现片上堆叠芯片,集成不同工艺、结构和用途的芯片。

现在,Mahajan正通过与DARPA、国防部和其他希望了解未来高效性能和设备的团体合作,期待组件层面的可能性和局限性。对于Mahajan来说,互联并行的概念已经初步确定,但会变得更加崎岖。马哈詹说:“关于这个广泛而缓慢的并行和串行问题,已经有了很多思考。并行链路的限制之一是需要复杂的封装,这存在产量和成本的问题。但是,如果您能让所有这些功能协同工作,就可以提供高带宽、低延迟连接和低功耗。”

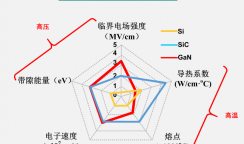

高密度的挑战在异构时代变得更加迫切,即集成的平衡。在设备上实现最高的能效和性能并不容易。Mahajan介绍,虽然未来会有一些很有前景的技术,但他预测硅技术可能会在2050年走到尽头。

有人认为5nm可能是这条路的尽头。包括Mahajan在内的乐观主义者认为是3nm。

“如果你说这些互联的重点是让每一代的带宽翻倍,我们还是在第一代和第二代之间。我们至少还有三代。从概念上讲,每一代可以持续两到三年。这给了我们至少10-15年的时间。就产品而言,我们的汽油要到2060年才会用完。即使这样,我们可能会用完缩放功能,但不会用完缩放功能。我们可以继续堆叠乐高,建造更复杂的结构,前提是产量得到控制。”

“从整体来看,我们已经在不同的硅工艺上实施和优化了不同的IP,并将它们集成到封装中。最终结果必须尽可能接近SoC执行。我们的重点是如何开发一种互连方法,使这些芯片以紧凑的方式连接到一个封装上,并通过清洁的电力传输进行冷却,并且封装互连和组件之间的互连不会限制封装的性能。”

增加天线密度是Mahajan团队的主要问题,但随着它继续缩小,即使失去动力。他们仍然有足够的未来证据来知道如何过渡到纯铜互连,从而创建3D堆栈和连接EMIB类型的连接。

要实现2050年(或2030年)的目标,需要在热管理和电力传输等技术领域采取渐进的步骤,但最终成本将占主导地位。

当被问及未来的RD战略时,马哈詹说:“在热管理方面,我们必须密切关注。这就需要将不同类型的模具温度保持在最佳水平,并将它们整合在一起,使它们更加紧密。我们可以改进材料,研究如何传播热量并带走热量。”此外,随着所有不同模具的电力传输网络集成在一起,这些架构将需要更智能的设计,他补充说。

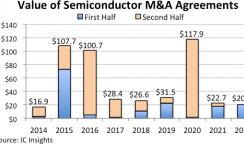

虽然时间表已经延长到2050年,但上述创新都不会牺牲性能、通信或成本。还有一个问题。在如此严格的限制下,英特尔或其他芯片制造商如何保持扩张?

马哈詹:“这很难预测,但英特尔做生意的方式是增加产量,并采取渐进措施保持密度不断增加。就像我们很难预测何时会耗尽经济天然气或基础设施一样,重点是产量和规模。”

“如果规模能带来成本优势,产出能让你做得更好,那么这两点会推动我们前进。我们可以通过专注于工程来控制成本,但技术的优势会超过成本。”

在线

在线

咨询

咨询

关注

关注